Profile Summary

Hi! I'm RAKESH GOGULA

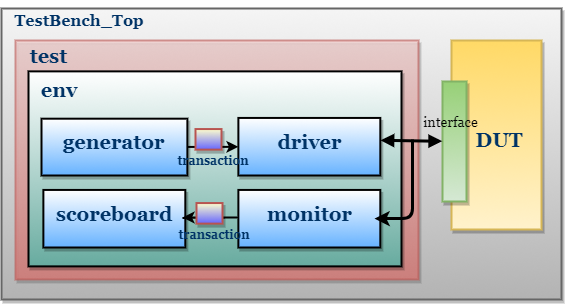

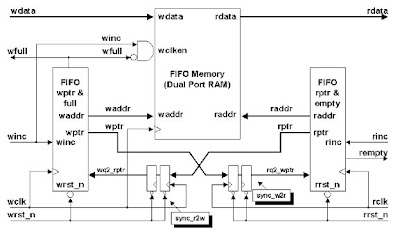

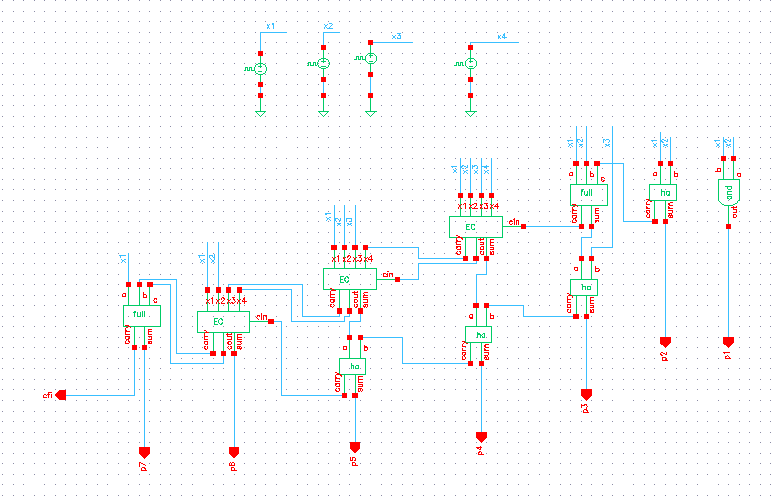

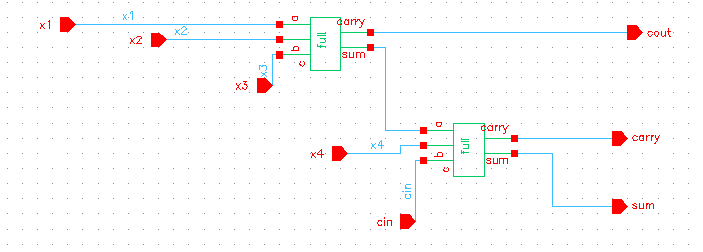

I am a fresher trainee seeking a challenging position in core engineering domains where I can apply my academic knowledge and technical skills to build a strong career foundation. I have a solid understanding of Digital System Design, Verilog, SystemVerilog, and am proficient in MS Office, with strong problem-solving abilities. My goal is to contribute to innovative and cutting-edge designs in the semiconductor industry while continuously enhancing my expertise.